Key Takeaways Box

- Architectural Independence: Utilizes the open-source RISC-V instruction set, saving millions in potential licensing fees and democratizing design access for local startups.

- Strategic Scope: Deliberately targets critical 5G networks, IoT gateways, and industrial infrastructure over consumer smartphones, prioritizing national security.

- Advanced Specifications: A 64-bit, dual-core processor running at 1.0 GHz, featuring out-of-order execution, advanced branch prediction, and full Linux OS support.

- Policy Driven Growth: Represents a major commercial milestone of the DIR-V program and is heavily supported by the financial frameworks of the India Semiconductor Mission (ISM) 2.0.

- Future Ready Roadmap: Establishes the robust technological stage for upcoming quad-core commercial chips and high-performance computing (HPC) domestic supercomputing processors.

Silicon chips are the invisible engines driving modern civilization. They dictate the trajectory of hypersonic missiles, manage the flow of national power grids, and process the infinite streams of data within our smartphones.

Historically, the ability to design and manufacture these microscopic marvels has been concentrated in the hands of a few global superpowers. This concentration leaves emerging economies highly vulnerable to supply chain disruptions, export controls, and astronomical licensing fees.

India has actively consumed roughly twenty percent of the world’s microprocessors while designing almost none of them domestically. The launch of the Dhruv64 microprocessor marks a definitive end to this era of total dependency.

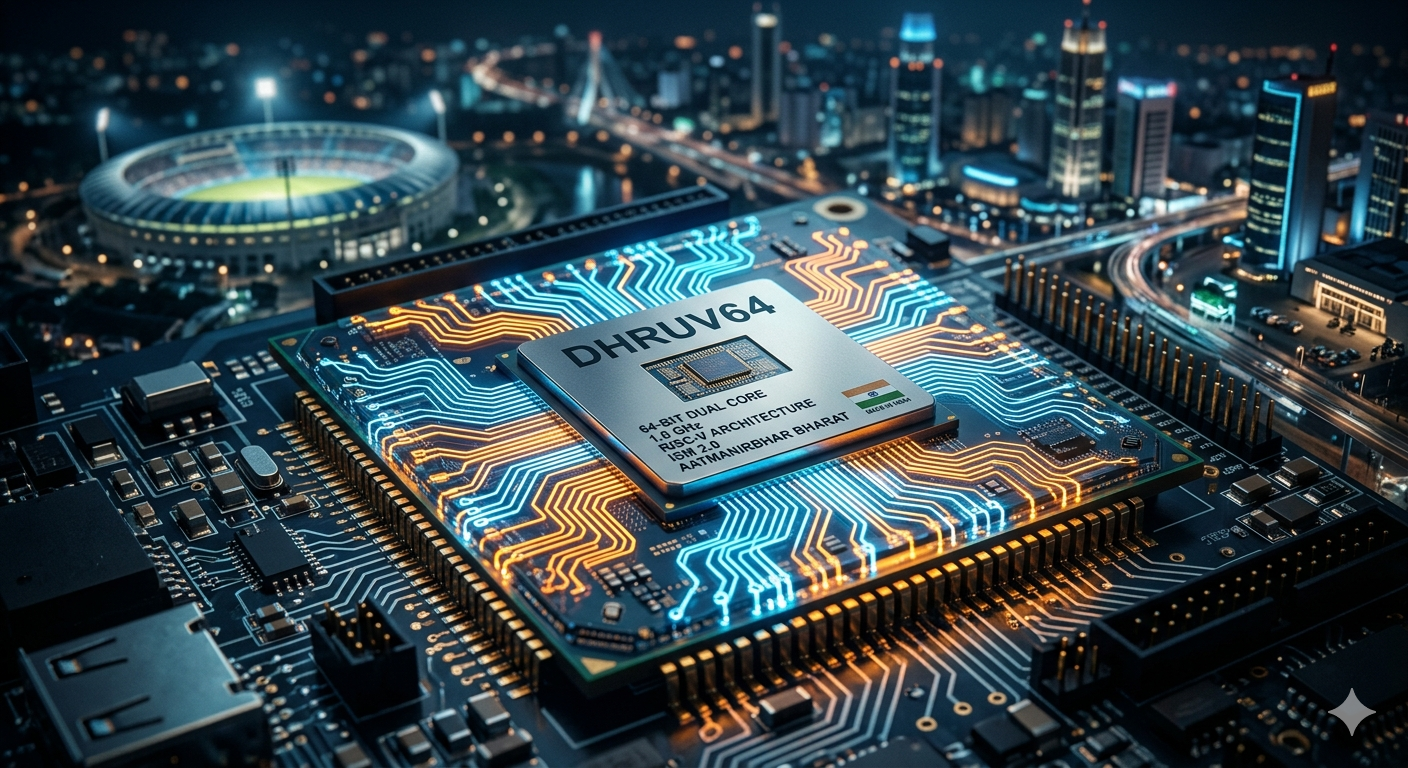

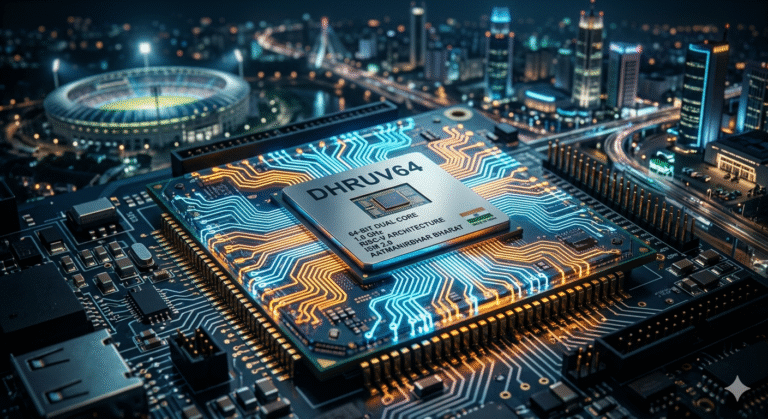

Developed entirely within the country by the Centre for Development of Advanced Computing (C-DAC), Dhruv64 is India’s first fully indigenous 1.0 GHz, 64-bit dual-core processor. This development operates as a powerful strategic declaration in the geopolitical arena.

By successfully engineering an application-class processor based on the open-source RISC-V architecture, the nation is actively dismantling its reliance on foreign proprietary designs. This analysis decodes the architectural intricacies of the Dhruv64 chip, its critical role within the broader India Semiconductor Mission (ISM), and the profound implications it holds for global technology supply chains.

Why This Topic Matters Today

The global semiconductor market is undergoing a structural transformation of unprecedented scale. Industry projections suggest the global market will reach the one trillion dollar mark by the end of the decade.

Simultaneously, the domestic Indian semiconductor market is projected to skyrocket from a valuation of approximately $50 billion today to an estimated $300 billion by the year 2035. This exponential growth is driven primarily by the rapid adoption of artificial intelligence, the electrification of automotive systems, and the expansion of massive data centers. tribuneindia

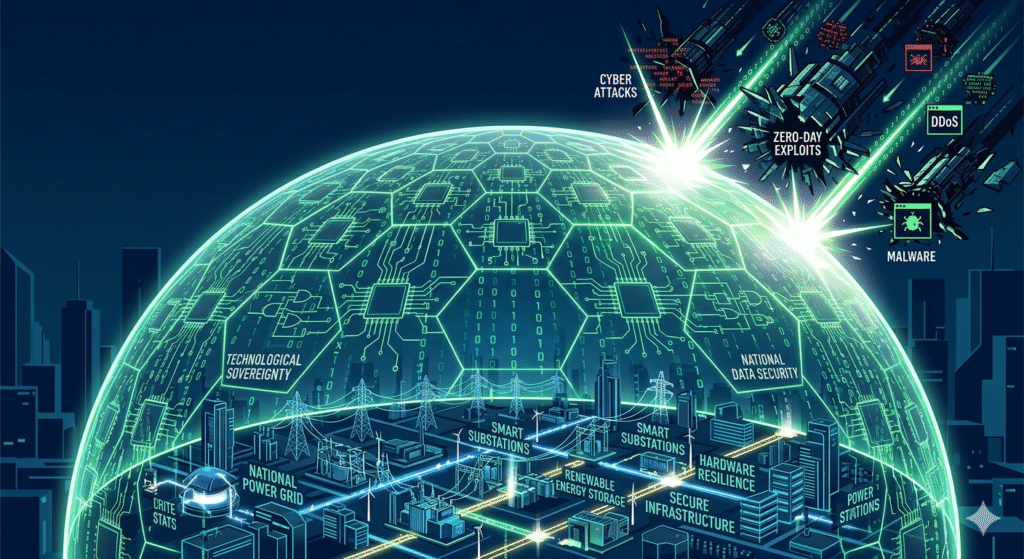

Currently, India imports over ninety percent of its semiconductor requirements, creating a massive economic and security vulnerability. Relying on foreign silicon for critical infrastructure like 5G telecommunications and defense systems introduces the severe risk of undocumented hardware backdoors or remote kill-switches.

Understanding the Dhruv64 microprocessor is essential because it represents the transition from a policy of mere consumption to active technological sovereignty.

For professionals engineering the next wave of smart devices, establishing foundational knowledge about why everyone should be educated in technology and its future aspects is critical for adapting to this domestic hardware revolution. Policymakers, industry leaders, and researchers must grasp the mechanics of indigenous silicon to navigate the upcoming decades of digital transformation effectively.

Key Highlights

The significance of the Dhruv64 processor extends far beyond its physical circuitry. The table below outlines the foundational elements that make this development a national milestone.

| Feature Area | Strategic & Technical Highlights |

| Architectural Foundation | Built entirely on the open-standard RISC-V (RV64IMAFD) instruction set, eliminating costly dependency on proprietary, licensed architectures like ARM or x86. |

| Performance Profile | Operates as a 64-bit, dual-core processor at 1.0 GHz with out-of-order execution, classifying it as an application-grade chip rather than a basic microcontroller. |

| Strategic Target Sectors | Engineered specifically for 5G infrastructure, smart energy meters, automotive systems, and industrial IoT, rather than consumer smartphones. |

| Policy Integration | Serves as the flagship deliverable of the Digital India RISC-V (DIR-V) initiative, aligning directly with the financial and strategic goals of the India Semiconductor Mission 2.0. |

| Ecosystem Enablement | Provides a royalty-free silicon foundation that empowers domestic startups and academic institutions to prototype hardware without prohibitive foreign licensing barriers. |

Background / Context

To fully appreciate the arrival of Dhruv64, one must examine the turbulent historical trajectory of India’s semiconductor ambitions.

Decades ago, India possessed a promising foundation for semiconductor fabrication. However, a devastating fire at the Semi-Conductor Laboratory (SCL) in Mohali in 1989 crippled the nation’s domestic fabrication capabilities.

This catastrophic event forced the country to rely entirely on imported electronics for decades, even as it cultivated a massive workforce of software engineers and chip designers who primarily served foreign multinational corporations. India currently houses twenty percent of the world’s chip design engineers, yet historically failed to capture the intellectual property value of their work.

The landscape began to shift dramatically with the inception of the Microprocessor Development Programme (MDP) guided by the Ministry of Electronics and Information Technology (MeitY).

This momentum accelerated in 2022 with the launch of the Digital India RISC-V (DIR-V) program. The core objective of DIR-V is to achieve industry-grade silicon and commercial design wins by leveraging the open-source RISC-V architecture. RISC-V allows engineers to design complex hardware without paying exorbitant royalties to established corporate giants, effectively democratizing silicon design. india-briefing

Parallel to these design efforts, the government introduced the India Semiconductor Mission (ISM). The initial phase, ISM 1.0, focused heavily on attracting large-scale foreign foundries and establishing a basic manufacturing footprint.

The recently announced ISM 2.0 represents a crucial pivot. With a robust budgetary provision of Rs. 1,000 crore for FY 2026-27 out of an Rs. 8,000 crore total outlay, ISM 2.0 shifts the focus toward producing semiconductor equipment domestically, designing full-stack Indian intellectual property, and fortifying the raw material supply chain. Dhruv64 is the direct manifestation of this matured design ecosystem, building upon the foundational work of its predecessors, the 32-bit and 64-bit THEJAS processors.

Did You Know? The smartphone business is the largest consumer of the global semiconductor industry. Semiconductors account for approximately 25-30% of a typical smartphone’s entire Bill of Materials (BoM), highlighting the massive economic drain when a nation imports all its chips.

Core Explanation

Understanding the mechanics and purpose of Dhruv64 requires breaking down its identity, functionality, and the organizations driving its deployment.

What It Is

The Dhruv64 is an indigenously developed System-on-Chip (SoC) operating as a 1.0 GHz, 64-bit dual-core microprocessor.

It is crucial to define what Dhruv64 is not. It is not intended to compete with the bleeding-edge chips found in high-end consumer mobile devices or graphics processing units from companies like NVIDIA or Apple.

Instead, it is designed as the reliable digital plumbing meant for compute-intensive embedded systems, industrial automation, and highly secure networking equipment. It is categorized as an application-class processor, bridging the gap between simple low-frequency microcontrollers and high-end server computing.

How It Works

The processor relies on the VEGA AS2161 core logic architecture.

When complex data or software instructions are fed into the system, they are processed through a highly sophisticated 16-stage out-of-order execution pipeline.

Simpler in-order processors execute software instructions strictly sequentially, which can lead to processing bottlenecks if one instruction is delayed waiting for memory. Dhruv64 bypasses this limitation. It actively analyzes the instruction stream and dynamically executes independent instructions as computing resources become available, vastly improving overall multitasking efficiency and system performance.

Key Components / Stakeholders

The realization of the Dhruv64 involves a highly coordinated matrix of academic, governmental, and industrial stakeholders.

- C-DAC (Centre for Development of Advanced Computing): Serving as the primary architectural and design force, C-DAC is responsible for the entire VEGA core series and the underlying logic design of the Dhruv64 SoC.

- MeitY (Ministry of Electronics and Information Technology): This ministry acts as the regulatory and funding body spearheading both the Microprocessor Development Programme and the DIR-V programs.

- Fabrication Partners: While the logic design is fully indigenous, physical manufacturing currently requires advanced fabrication plants. Dhruv64 was taped out on a 28-nanometer process node. Reports indicate this physical fabrication involved overseas foundries, specifically Silterra in Malaysia, due to the ongoing construction of advanced-node domestic fabs in India.

Conceptual Breakdown

To truly evaluate the processing prowess of Dhruv64, engineers must look beneath the silicon surface into its highly structured microarchitecture. The specifications read like a robust blueprint for industrial-grade computing.

The foundational architecture is based on the RISC-V 64G (RV64IMAFD) instruction set. This specific acronym designates comprehensive hardware support for Integer processing (I), Multiplication and Division algorithms (M), Atomic instructions for memory synchronization (A), Single-precision Floating-point calculations (F), and Double-precision Floating-point mathematics (D).

This comprehensive mathematical support ensures the processor can handle the complex algorithms required by modern automation systems without relying on slower software-based calculations.

The chip incorporates a Harvard architecture design. By utilizing entirely separate memory pathways and dedicated caches for instructions and data, the processor effectively eliminates the classic Von Neumann bottleneck. The CPU can fetch an upcoming software instruction simultaneously while reading or writing data, significantly increasing throughput.

Perhaps the most critical feature differentiating Dhruv64 from simple microcontrollers is its hardware Memory Management Unit (MMU). The inclusion of a robust MMU enables page-based virtual memory. This architectural feature means Dhruv64 can natively run full-fledged, complex operating systems like standard Linux, making it highly versatile for network servers and advanced edge computing.

To keep its 16-stage pipeline constantly fed with data, the chip utilizes advanced branch prediction mechanisms. It integrates a Branch Target Buffer (BTB), a Branch History Table (BHT), and a Return Address Stack (RAS). These components allow the processor to intelligently guess the outcome of logical software branches before they officially occur, drastically reducing idle processing latency.

Finally, the processor features an AXI4 / ACE-compliant external interface. This widely adopted industry standard ensures that system designers can easily integrate Dhruv64 with peripheral hardware, networking sensors, and external FPGAs without requiring extensive custom engineering workframes.

Expert Tip: When evaluating processors for critical industrial applications, sheer clock speed is secondary to interface breadth and operating voltage. Dhruv64’s 1.8 V I/O standard makes it exceptionally compatible with rugged industrial sensors and manufacturing equipment, unlike the fragile, low-voltage logic gates used in consumer smartphone chips.

Real-World Examples / Case Studies

The application spectrum for an application-class chip like Dhruv64 is vast, particularly in sectors where data security, hardware reliability, and longevity supersede raw graphical processing power.

The modernization of national power grids relies heavily on smart energy meters. Millions of these utility meters require secure, low-cost processing to transmit consumption data accurately. Utilizing an indigenous processor like Dhruv64 prevents the catastrophic risk of foreign spyware or remote kill-switches being embedded in critical infrastructure.

Industrial automation and the Internet of Things (IoT) represent another massive deployment vector. Smart factories rely on deterministic processors to control robotic arms, monitor assembly lines, and process sensor data locally without cloud latency.

The aviation and logistics sectors are actively deploying vast networks of interconnected devices. Advanced systems, such as those relying on(https://blog.aquartia.in/index.php/2025/03/21/iot-in-airports-smart-luggage-tracking-seamless-check-in/), require robust edge-computing processors that can securely handle high volumes of RFID and Bluetooth Low Energy (BLE) tag data in real-time. Dhruv64 provides the exact intermediate computing power necessary for these decentralized edge gateways, ensuring data is processed quickly before being sent to centralized servers.

Furthermore, earlier variants of the VEGA processor family have already proven their viability in practical applications. C-DAC has successfully deployed RISC-V based chips in prototypes for affordable hearing aids and vital-sign monitors. The inherent flexibility of the RISC-V architecture allowed designers to tune the processors for ultra-low power consumption, which significantly extends the battery life of these critical medical devices.

Similarly, agricultural drone technology benefits from these localized chips, aiding in precise field monitoring and optimizing fertilizer distribution without relying on expensive, proprietary hardware imports.

Benefits / Advantages

The strategic transition from importing commercial off-the-shelf processors to deploying the indigenous Dhruv64 yields multifaceted advantages for the entire technological ecosystem.

The most immediate financial benefit is the complete elimination of licensing constraints. Proprietary architectures like ARM or x86 require companies to pay millions of dollars in upfront licensing fees before a single physical chip is ever manufactured.

Because RISC-V is an open standard, this massive barrier to entry is obliterated. This democratization allows cash-strapped academic institutions, nascent hardware startups, and mid-sized enterprises to design custom silicon tailored to their specific needs without seeking permission from foreign intellectual property holders.

Absolute hardware security is another paramount advantage. Black-box processors procured from foreign vendors can harbor undocumented backdoors or hardware trojans designed to leak data or sabotage systems during geopolitical conflicts.

By designing the Register Transfer Level (RTL) code domestically, national defense agencies, space exploration programs, and government utilities can meticulously audit every single transistor pathway. This ensures the foundational hardware is absolutely free of malicious anomalies.

Furthermore, the development of Dhruv64 acts as a massive catalyst for talent incubation. As noted earlier, India boasts an estimated twenty percent of the global chip design workforce. Programs surrounding the Dhruv64 actively redirect this immense talent pool away from foreign multinational corporations and toward domestic intellectual property creation.

This ensures that the economic value generated by Indian engineers remains within the domestic economy, fortifying national supply chain resilience against future global disruptions.

Challenges

Despite the monumental achievement of designing the chip, the domestic ecosystem faces undeniable structural and operational hurdles that must be addressed to translate design prowess into large-scale industrial dominance.

The most glaring bottleneck is the physical fabrication process. Designing a sophisticated logic chip is only half the battle; printing those microscopic circuits onto a silicon wafer is highly complex and capital-intensive.

Currently, India lacks commercial advanced-node fabrication facilities capable of printing chips at scale. Consequently, the Dhruv64, which operates on a 28-nanometer node, had to be taped out in overseas foundries located in Taiwan and Malaysia. Until the multi-billion dollar domestic fabrication plants incentivized under the India Semiconductor Mission become fully operational, India remains heavily dependent on foreign manufacturing pipelines.

Additionally, there is a reality check required regarding raw performance capabilities. V. Kamakoti, Director of IIT Madras and a pioneer of the Shakti processor, accurately described the current crop of indigenous chips as operating at a “generation minus one” or “generation minus two” level compared to the absolute bleeding-edge commercial giants.

To contextualize this, a 1.0 GHz dual-core profile is roughly comparable to the processing engines found in high-end smartphones from the year 2011, such as the Apple A5 or the Samsung Exynos 4210. While perfectly adequate for industrial routing and smart meters, it lacks the raw horsepower to power modern AI-driven consumer applications or advanced graphics processing.

Finally, overcoming ecosystem inertia remains a profound challenge. The global tech industry is deeply entrenched in established architectures with decades of optimized software libraries and developer tools. Convincing commercial hardware manufacturers to transition their product lines from trusted, mature platforms like ARM to a newly established domestic RISC-V platform requires immense financial incentives, extensive developer support, and proof of absolute reliability over an extended period.

Global Implications

The emergence of the Dhruv64 microprocessor must be viewed through the lens of modern techno-geopolitics. In the twenty-first century, semiconductors operate as the new strategic oil.

Recent legislative maneuvers, such as the United States’ CHIPS Act and stringent, targeted export controls restricting advanced artificial intelligence chips from reaching China, clearly demonstrate how silicon supply chains are actively weaponized for geopolitical leverage.

By deliberately cultivating an indigenous RISC-V ecosystem, India strategically maneuvers to avoid becoming collateral damage in the escalating tech wars between dominant global superpowers. The policy thrust codified under the India Semiconductor Mission 2.0 specifically targets the creation of a robust domestic design environment.

The government has allocated significant funds toward the Design Linked Incentive (DLI) scheme. This specific policy mechanism is designed to financially support fabless semiconductor startups, offsetting the massive costs of prototyping and testing. The stated long-term goal of the Ministry of Electronics and Information Technology is to breed global tech giants—equivalent to an Indian Qualcomm or AMD—directly on domestic soil.

Furthermore, global technological powers increasingly view India as a trusted, neutral node in the global supply chain. Formal partnerships, such as the Memorandum of Understanding signed with the European Union regarding semiconductor supply chain resilience, and collaborative ventures integrating Japanese precision manufacturing expertise, signal a strong willingness from the international community.

These alliances aim to integrate India deeply into a newly decentralized, highly resilient global semiconductor manufacturing network, reducing global reliance on highly concentrated manufacturing hubs in East Asia.

Future Trends

The release of the Dhruv64 processor represents a critical stepping stone, not the final destination. The developmental roadmap laid out by C-DAC and MeitY is both aggressive and systematically structured to capture increasing market share.

Following the deployment of Dhruv64, the ecosystem will introduce the highly anticipated Dhanush processor series. The immediate successor, DHANUSH64, will feature a quad-core architecture running at 1.2 GHz on the same reliable 28-nanometer fabrication node.

This will quickly be followed by the more advanced DHANUSH64+ variant, which aims to target faster 2.0 GHz speeds utilizing smaller, more efficient 14-nanometer or 16-nanometer process technologies. These upcoming iterations will expand India’s homegrown ecosystem into higher-end commercial applications.

Looking further down the timeline, the long-term trajectory established by C-DAC targets the development of an octa-core processor by 2026. Eventually, as high-performance computing (HPC) research converges with standard microprocessor programs, the government aims to scale architectures up to massive 48-core or 64-core chips. These powerful processors are intended specifically to drive domestic supercomputing grids, advanced telecommunications servers, and data centers.

Market projections firmly support this aggressive development cycle. Analytical reports from Deloitte indicate that domestic semiconductor demand will evolve significantly, driven primarily by data centers, computing, and the electrification of the automotive sector.

To meet this surging demand, the physical landscape of Indian manufacturing will undergo a radical overhaul. Forecasts suggest that by 2035, India will successfully host up to five large-scale silicon fabrication units (fabs), ten specialized compound semiconductor fabs, and up to twenty-five Outsourced Semiconductor Assembly and Test (OSAT) facilities, ultimately meeting sixty percent of the nation’s demand through localized production.

Comparison Table

To contextualize the evolution and positioning of the Dhruv64 within the broader indigenous semiconductor ecosystem, the following table tracks the technical progression of India’s homegrown processor timeline.

| Processor Name | Release/Target | Core Architecture | Cores | Clock Speed | Fabrication Node | Primary Application |

| THEJAS32 | 2022 | 32-bit RISC-V | Single | 100 MHz | 130nm | Basic IoT, Education, Sensors |

| SHAKTI (C-Class) | 2018 | 64-bit RISC-V | Single | 1.2 GHz | 28nm | Secure microcontrollers |

| THEJAS64 | 2023 | 64-bit RISC-V | Single | 100 MHz | 180nm | Industrial Automation |

| DHRUV64 | 2025 | 64-bit RISC-V | Dual | 1.0 GHz | 28nm | 5G, Smart Grids, Edge Compute |

| DHANUSH64+ | 2026/27 (Est) | 64-bit RISC-V | Quad | 2.0 GHz | 14/16nm | High-end embedded systems |

Conclusion

In the intensely competitive grand chessboard of global technology, raw computational speed is heavily publicized, but strategic autonomy is what truly guarantees a nation’s long-term security and economic prosperity. The creation of the Dhruv64 microprocessor is a masterstroke of geopolitical and engineering pragmatism.

By deliberately choosing to target the foundational, heavy-lifting layer of industrial and infrastructural computing through an open-source architecture, India is actively insulating its most critical digital arteries. As the highly funded India Semiconductor Mission 2.0 pumps essential capital into deep-tech indigenization, and the nation moves steadily toward its 2035 vision of a $300 billion self-reliant tech ecosystem, Dhruv64 will stand as a monumental catalyst.

It will be remembered not necessarily as the fastest silicon chip of its era, but definitively as the processor that irrevocably shifted the geopolitical gravity of global silicon design toward the Indian subcontinent.

FAQ SECTION

1. What exactly is the Dhruv64 microprocessor? Dhruv64 is India’s first fully indigenous 64-bit, dual-core microprocessor. Designed by C-DAC under the Ministry of Electronics and Information Technology (MeitY), it operates at a clock speed of 1.0 GHz. It is engineered specifically to power critical digital infrastructure, industrial automation, and highly secure IoT devices without relying on foreign proprietary designs.

2. Which core architecture does Dhruv64 utilize? The processor is built on the open-source RISC-V 64G (RV64IMAFD) instruction set architecture. Adopting this open standard means that Indian developers and hardware manufacturers do not have to pay expensive licensing royalties to foreign entities like ARM or Intel, which aggressively fosters innovation and cost-effectiveness for domestic startups.

3. Is Dhruv64 designed to rival chips from Intel, Apple, or Qualcomm? No, Dhruv64 is not designed to compete directly with high-end consumer smartphone processors or gaming graphics cards. It operates as an application-class processor designed for absolute reliability and security in sectors like 5G networking infrastructure, smart utility meters, automotive systems, and defense hardware, where systemic resilience is valued over sheer benchmarking speed.

4. Where is the physical Dhruv64 chip manufactured? While the silicon logic was completely designed in India by C-DAC engineers, the physical fabrication (known as taping out) occurred overseas at 28-nanometer process foundries located in countries like Malaysia (Silterra) or Taiwan. India is currently in the process of building its own domestic fabrication capabilities under the India Semiconductor Mission.

5. Can the Dhruv64 run advanced operating systems like Linux? Yes, it is fully capable of running advanced software. Unlike simpler microcontrollers, Dhruv64 features a full hardware Memory Management Unit (MMU) combined with page-based virtual memory support. This critical architectural inclusion allows the processor to natively support and run complex operating systems like standard Linux, making it highly versatile for network servers.

6. What is the overarching purpose of the DIR-V program? The Digital India RISC-V (DIR-V) Microprocessor Program was officially launched in 2022 by the Government of India. Its primary goal is to actively catalyze the domestic semiconductor ecosystem, enabling the mass production of next-generation indigenous microprocessors for both domestic and global markets using the open-source RISC-V framework.

7. How does Dhruv64 differ from the older Shakti processor? Both are highly capable indigenous processors based on the RISC-V architecture. However, the SHAKTI series was developed primarily by IIT Madras starting around 2018, featuring mostly single-core designs targeting secure microcontrollers. Dhruv64, developed by C-DAC, represents a significant progression to dual-core, out-of-order processing meant for heavier application-class computing workloads.

8. What are the government’s future microprocessor plans after Dhruv64? C-DAC’s development roadmap is advancing rapidly. The direct successors to Dhruv64 are the Dhanush and Dhanush+ processors. Dhanush64 will operate as a quad-core chip running at 1.2 GHz, while Dhanush64+ will aggressively scale up to 2.0 GHz speeds utilizing a smaller 14/16nm fabrication node. Eventually, the roadmap targets 64-core processors for advanced supercomputing.

9. What role does ISM 2.0 play in this semiconductor ecosystem? The India Semiconductor Mission (ISM) 2.0 represents the next massive phase of the government’s hardware strategy, equipped with an Rs. 8,000 crore total financial outlay. It specifically focuses on localizing semiconductor equipment manufacturing, developing raw material supply chains, nurturing a fabless startup ecosystem, and offering Design Linked Incentives (DLI) to support IP creation.

10. Why is indigenous chip development considered crucial for national security? Imported commercial microprocessors can contain undocumented software vulnerabilities or deliberate hardware backdoors. By controlling the processor design at the Register Transfer Level (RTL) through chips like Dhruv64, the government ensures that critical sectors like defense communications and power grids remain totally secure from foreign espionage and supply chain weaponization.

+ There are no comments

Add yours